LLC 谐振变换器中薄膜型集成磁件的研究

1 引言

大规模集成电路技术的发展,对高功率、低造型、高效率的电源需求越来越迫切。传统的 PWM 拓扑限制了高功率密度的获得。这时,发明了 LLC 谐振电路以获得所期望的特性。有文献证明[1],LLC 谐振变换器能够减少 40% 的总损耗。本文结合前人提出的 LLC 拓扑,应用磁集成技术将 LLC 电路中的磁件集成到一个磁芯上,以达到进一步减少磁件体积,重量和高度以及减少电流纹波的目的,同时对集成磁件进行了薄膜化设计。

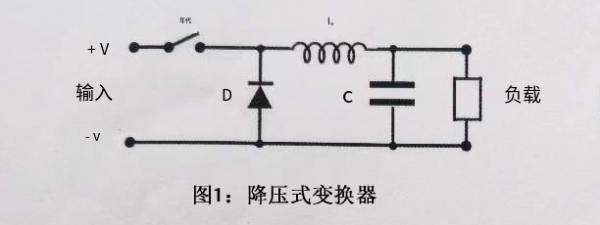

图 1 所示即为 LLC 谐振变换器的电路原理图。由图 1 可见,若没有励磁电感 Lm,这个变换器和串联谐振变换器相同,加上 Lm 后,这个电路的工作特性及工作方式就完全不同了。电路中有三个无源元件:Lm,Lr 和 Gr,副边是一个带中心抽头的整流电路,后接一个滤波电容,原边是一个半桥电路,也可以用全桥和其他电路结构代替。

2 LLC 集成变换器的原理分析

为进一步减小变换器中磁件的损耗、体积,本文提出 LLC 集成变换器,如图 2 所示电感绕组绕制在1柱,其对应的磁通为 φ1,变压器绕制在 3 柱,对应磁通为 φ3;公共磁柱即 2 柱磁通为 φ2。磁集成的目的是要减小磁件的损耗、体积、重量和改善滤波效果。原理图 1 中的 LT 结构与考虑了原边漏感以及励磁电感的双绕组变压器等效模型结构相似。但是由于漏感控制非常困难,而图中谐振电感Lr的值对于谐振变换器是非常关键的因素。故增加一个电感线圈,漏感和增加的电感线圈等效成一个新的谐振电感Lr,Lm为变压器的励磁电感。所以在考虑LLC谐振变换器的磁性元件集成的时候,只需要考虑一个电感和一个变压器的集成就可以了。

2.1 集成磁件的等效电路

利用磁路中的对偶关系,以及法拉第电磁感应定律能导出图示的等效电路图[6]。

(a)根据磁路欧姆定律,得到图中集成磁件的等效磁路模型,NL,NP,Ns,Ns,IL,IP,I1,I2分别是ab,cd,ef,fg绕组的匝数和电流。R1,R2,R3分别是三个磁柱上的磁阻。集成磁件的等效磁路模型及参数见图3(a)。

(b)根据磁路与电路的对偶关系,得出磁路模型的对偶图,如图3(b)。

(c)然后对对偶图进行尺度变换,最后根据尺度变换后的电路,以便于应用法拉第电磁感应定律以及变压器的阻抗变换原理得到等效电路图。尺寸变换后的电路如图3(c)所示。

(d)如图3(d)所示为集成磁件的等效电路图。

2.2 集成磁件的两种工作模式

根据工作时电路的不同,分两种模式简要讨论集成LLC谐振变换器的工作原理。

令

根据模式1得到:

;

由上述4个式子可以得出:

则

根据模式2,亦可列出类似方程,得:

为了得到和分立元件相同的值[2],可以使谐振电感Lr为14μH,励磁电感Lm为60μH。变压器绕组匝数比为16:4:4,NL=6,NP=10每个磁柱气隙为0.56mm。

3 LLC 集成变换器的薄膜化设计

磁性器件的薄膜化可以使立体三维结构的磁性器件向低维的平面结构发展,大大减小元器件的尺寸,并且随着多种低损耗、高电阻率、高饱和磁导率、高起始磁导率、宽工作温度范围的高频薄膜软磁材料的研制成功,使得制作高频磁性器件成为现实。这为实现开关电源的“短、小、轻、薄”提供了新的实现手段[3]。

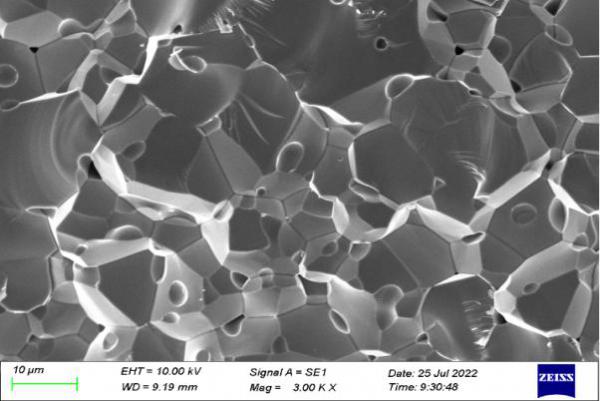

3.1 磁性材料的选择

薄膜材料和块材相比差异在于薄膜的厚度很薄。薄膜很薄时,一般为岛状结构,没有形成连续的薄膜,就像许多粒状的集合,而在这种集合中各粒状之间的交换作用比较微弱,当受热扰动时便显示出超顺磁性,在一般真空条件下制得的薄膜,粒状性比较高,而在高真空条件下,粒状性比较低,因此在制作薄膜器件时要注意控制厚度来获得最佳的器件性能。

对于磁导率较高的材料或者是使用频率较高的情况,趋肤效应影响特别严重,所带来的涡流损耗也特别大,因而提高材料的电阻率是减小涡流损耗的主要途径,也是提高软磁薄膜性能的一个重要手段。

由于本变换器中电感线圈的励磁电流为一交变量,其正负半周的波形、幅值等都相同,故要求材料所具有的磁滞回线较窄。

文献[4]给出了一种较好的软磁材料CoNbZr。该材料所具备的优点:电阻率比较高,矫顽磁力Hc=1.83oe,饱和磁密Bs=1.25T,回线所包围的面积小,材料自身损耗小,是一种优良的磁薄膜材料。基于以上各种优点,本设计采用该种材料来制作铁芯。

3.2 薄膜电感结构的选择

薄膜电感不同的绕线形状的设计将会带来电感量的不同,占用基片面积大小的不同,以及决定着制作工艺的复杂程度。常见的电感的绕线的类型有栅极型薄膜电感,螺旋型薄膜电感,以及编织型薄膜电感。

综合各个绕线形式的优缺点[5],选用螺旋型绕线方式,绕线制作一般采用光刻或离子刻,考虑到成本以及制作难度,选用PCB的方式来制作电感绕组。PCB板不但可以制作单面板,而且还可以制作双面板,多层板,不但可以增加电感之间的耦合度,还可以在单位面积内获得高于单面两倍的电感量(由于L=L1+L2+2M),因而对于在更小的平面内获得更大的电感是一条极为有利的途径。图5所示为薄膜电感的绕组示意图。

3.3 薄膜变压器结构的选择

当前薄膜变压器的类型大致有下列几种:基于普通变压器原理的薄膜变压器、初次级绕组同轴排列的薄膜变压器、针孔型薄膜变压器。为了方便起见,薄膜变压器的结构选择初次级绕组同轴排列的薄膜变压器,其结构如图6所示。

变压器的基本原理类似双纽线线圈变压器的原理。初次级线圈同轴排列,磁力线从线圈上面的中心开始通向外侧,然后从下面返回中心。该变压器的变比取决于线圈的长度,即变压比和初次级线圈的长度一致,这样就可以通过多层线圈之间的相互连接方式的不同来控制变压比。另外,由于薄膜边缘临近效应的差异会导致磁力线走向和薄膜表面垂直,导致降低耦合系数,解决的办法就是增加线圈的层数。本文是用铁芯使得漏磁降低,耦合系数提高的。

3.4 电感绕组的设计

(1)铜箔的计算:;其中铜箔厚度h一般小于趋肤深度的两倍,j为电流密度,imax为最大电流,w为铜箔的宽度。

(2)绝缘介质的计算:绝缘介质的面积设定为单个电感绕组的面积大小,由可以确定绝缘介质的厚度hd。式中C为电容大小,ε0为真空介电常数,εr为介质的介电常数,AL为单个电感绕组面积的大小。

将上述两层薄膜电感作为一个基本单元,第一层的接线端子分别为al,bl,C1,d1。al,b1分别为上层的两个接线端子,c1,d1为下层的两个接线端子。每个基本单元的等效电路图如图7所示。

由于基本单元内两层绕组能产生电容,LLC谐振变换器中需要电容Cr,于是就想到利用这部分电容。因为每个单元两层绕组之间的介质厚度可以控制,因此通过适当调节,能够得到我们所需要的结果。根据1)计算,取铜箔宽度为2.5mm,导线间隔取0.5mm,厚度取0.105mm。根据2)算得每个单元两层绕组之间的距离为0.7mm。

3.5 薄膜变压器的设计

变压器原理示意图如图6,将两层这样的绕组做成一个基本单元,因为该种变压器的变比决定于绕线的长度,将上层外侧的绕组做原边,内侧绕组做副边,下层的外侧绕组做副边,外侧绕组做原边,上下层的原副边相连,这样每个单元的原副边的绕组长度就相等了,利用这种结构通过初次级绕组的串并联就能够得到任意变比的变压器。但是本文为了尽可能实现低高度,将薄膜集成磁件设计为两层,这为从工艺上实现本电路所要求的变比增加了难度。本文设计的变压器就只有一个基本单元,从副边绕组中间点抽出一个端子,将副边绕组两个端子连接在一起,这样就得到了2:1的变比,再从新副边绕组中间点抽出一个端子,这样就得到了变比为4:l:1的三绕组变压器。要求变压器绕组之间介质的介电常数尽量低,以减少寄生电容的存在,不至于影响Cr的大小。

3.6 薄膜集成磁件的设计

按照上述工艺要求即可做出满足电路需要的集成薄膜磁件,其铁心用射频磁控溅射沉积。考虑到根据集成磁件所确定的磁芯的形状会导致薄膜集成磁件边柱有较大的漏磁,故将原来平面化设计后的EI磁芯改变成为四型磁芯,具体结构如图8所示。

4 仿真验证

根据上述分析与推理,我们用Maxwell SV进行仿真。薄膜集成磁件的结构参数为:铜箔宽度为2.5mm,厚度为0.105mm,铜箔之间间隙为0.5mm,气隙为0.56mm,绝缘介质厚度为0.7mm,铁芯高度为5mm。仿真结果如图9(b)所示,图9(a)是采用传统的集成方法后经平面化设计的集成磁件的仿真图,通过对比,发现薄膜化设计以后高度进一步降低,并且降低的幅度较大,使得“短、小、轻、薄”的要求得到进一步的满足,这种低高度的集成磁件还能和SMT技术的发展相适应,使电力电子器件得以大规模工业化生产。另外,薄膜集成磁件的磁密较大,磁件的利用率较高,不过这可能会带来磁滞饱和的问题,由于本设计采用的是新型的磁性薄膜材料CoNbZr,其饱和磁密较高[4],为1.25T。这能够一定程度上缓解这个矛盾。

5 结语

本文通过对LLC谐振变换器进行磁件集成设计,通过分析导出了集成磁件的等效电路,讨论了其工作模式,给出集成磁件的设计结果,并且应用薄膜技术对集成磁件进行了薄膜化设计。最后给出了仿真结果。该设计显示出了较大的优越性,磁芯利用率较高,集成磁件的厚度仅为5mm,适应了SMT技术发展的要求,实现了LLC谐振变换器的“短、小、轻、薄”。

暂无评论